-

ARM11 编辑

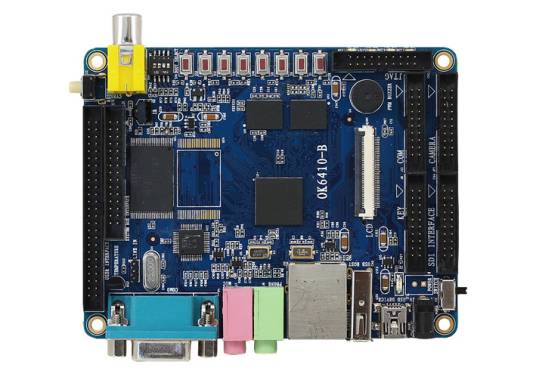

ARM11系列微处理器是ARM公司近年推出的新一代RISC处理器,它是ARM新指令架构——ARMv6的第一代设计实现。该系列主要有ARM1136J,ARM1156T2和ARM1176JZ三个内核型号,分别针对不同应用领域。

中文名:ARM11

外文名:ARM11

指令集:Thumb、E(DSP)

架构:Cache

工艺:0.13um

字长:64

最高频率:500M

功耗:0.4mW/MHz

ARMv6—决定性能的基础

ARMv6架构决定了可以达到高性能处理器的基础。总的来说,ARMv6架构通过以下几点来增强处理器的性能:

1.多媒体处理扩展 使MPEG4编码/解码加快一倍

音频处理加快一倍

2.增强的Cache结构

实地址Cache4

减少Cache的刷新和重载

减少上下文切换的开销

3.增强的异常和中断处理使实时任务的处理更加迅速

4.支持Unaligned和Mixed-endian数据访问 使数据共享、软件移植更简单,也有利于节省存储器空间

对绝大多数应用来说,ARMv6保持了100%的二进制向下兼容,使用户过去开发的程序可以进一步继承下去。ARMv6保持了所有过去架构中的T(Thumb指令)和E(DSP指令)扩展,使代码压缩和DSP处理特点得到延续;为了加速Java代码执行速度的ARM Jazalle技术也继续在ARMv6架构中发挥重要作用。

ARM11处理器的流水线和以前的ARM内核不同,它由8级流水线组成,可以比5级流水线的ARM9达到更高的运行频率。

从通常的角度说,过长的流水线往往会削弱指令的执行效率。一方面,如果随后的指令需要用到前面指令的执行结果作为输入,它就需要等到前面指令执行完。ARM11处理器通过forwarding来避免这种流水线中的数据冲突,它可以让指令执行的结果快速进入到后面指令的流水线中。另一方面,如果指令执行的正常顺序被打断(如出现跳转指令),普通流水线处理器往往要付出更大的代价,ARM11通过实现跳转预测技术来保持最佳的流水线效率。这些特殊技术的使用,使ARM11处理器优化到更高的流水线吞吐量的同时,还能保持和5级流水线(如ARM9处理器中的流水结构)一样的有效性。

跳转预测及管理

跳转指令通常都是条件执行的。问题在于那些决定是否跳转的条件要在跳转指令被译码的后3~4个周期才能就绪。如果不做特殊处理,跳转指令必须等待,这样使指令执行效率变得让人难以忍受。跳转预测就是用来帮助解决这种延迟的。ARM11处理器提供两种技术来对跳转作出预测—动态预测和静态预测。

动态预测:在ARM11处理器中包含了64个4状态跳转地址缓存器(4-state branch target address cache)来保存最近发生的跳转指令的结果。通过对这些历史纪录的查找,处理器可以预测出当前的跳转指令是否会被执行。

静态预测:当在动态预测的缓存器中无法查到和当前指令匹配的记录,ARM11处理器就从跳转的方式来判断是否执行。如果是向回跳转,大多数情况是遇到一个循环,处理器会假设这条指令被执行。如果是向前跳转,处理器会假设这条指令不被执行。

动态预测和静态预测的组合使ARM11处理器能达到85%的预测正确性,对于每一个正确的预测,给指令执行带来的是减少5个时钟周期的等待时间。

增强的存储器访问

在ARM11处理器中,指令和数据可以更长时间的被保存在Cache中。一方面是由于物理地址Cache的实现,使上下文切换避免了反复重载Cache,另一方面是由于ARM11的Cache还有很多其它新颖的技术特点。

如果数据的访问引起了CacheMiss,Cache将到存储器中读取需要的数据。但是ARM11处理器的流水线并不会停止下来。只要后面的指令没有用到Cache Miss将读回来的数据,ARM11处理器就会继续执行下去。即使下一条指令还是存储器访问指令,只要数据存放在Cache中,ARM11也会允许这条指令被执行。只有这条指令又引起一次CacheMiss,处理器才会停止下来。在大多数应用中,经过编译器调配后,这种情况并不多见。

流水线的并行机制

尽管ARM11是单指令发射处理器,但是在流水线的后半部分允许了极大程度的并行性。一旦指令被解码,将根据操作类型发射到不同的执行单元中。ARM11的数据通路中包含多个处理单元,允许ALU操作、乘法操作和存储器访问操作同时进行。

考虑到不同的指令需要不同的执行时间,当三类指令先后被发射到流水线中,它们就可以同时被执行。而且ARM11处理器允许指令的乱序完成,如果在指令之间没有数据的相关性,所有指令都可以不必等待前面的指令完成而结束自己的执行。

64位的数据通道

在绝大多数的应用中,一个真正的64位处理器,在功耗面积的成本上还是不经济的。ARM11处理器展示了一种以32位处理器的成本,提供64位处理器性能的解决方案。ARM11处理中,内核和Cache,及协处理器之间的数据通路是64位的。这使处理器可以每周期读入两条指令或存放两个连续的数据,以大大提高数据访问和处理的速度。经过评测,这已经和64位处理器的性能相差无几。

浮点运算

ARM11处理器将浮点运算当成一个可供用户选择的设计。用户可以在向ARM要求授权的时候选择是否包括浮点处理器的内核。在流水线上的重要区别不仅是为了达到更高的性能,还是从实现的角度来考虑的。所以,ARM11内核在运行于极高频率的同时,也能非常容易的被集成在SoC设计中。同时,ARM11处理器提供的向上兼容性,使OEM可以放心的选用任何基于ARM的产品。

此外,ARM11的成功还得益于ARM完整的开发环境和广泛的IP解决方案,以及不断扩大的ARM开发者和合作伙伴联盟。

ARM公司近日公布了四个新的ARM11系列微处理器内核(ARM1156T2-S内核、ARM1156T2F-S内核ARM1176JZ-S内核和ARM11JZF-S内核),以及应用于ARM1176JZ-S 和ARM11JZF-S内核系列的PrimeXsys平台、相关的CoreSight技术。

ARM1156T2-S和ARM1156T2F-S内核都基于ARMv6指令集体系结构,将是首批含有ARM Thumb-2内核技术的产品,可令合作伙伴进一步减少与存储系统相关的生产成本。两款新内核主要用于多种深嵌入式存储器、汽车网络和成像应用产品,提供了更高的CPU性能和吞吐量,并增加了许多特殊功能,可解决新一代装置的设计难题。体系结构中增添的功能包括:对于汽车安全系统类安全应用产品的开发至关重要的存储器容错能力。ARM1156T2-S和ARM1156T2F-S内核与新的AMBA 3.0 AXI总线标准一致,可满足高性能系统的大量数据存取需求。Thumb-2内核技术结合了16位、32位指令集体系结构,提供更低的功耗、更高的性能、更短的编码,该技术提供的软件技术方案较现用的ARM技术方案减少使用26%的存储空间、较现用的Thumb技术方案增速25%。

ARM1176JZ-S和ARM1176JZF-S内核及PrimeXsys平台是首批以ARM TrustZone技术实现手持装置和消费电子装置中公开操作系统的超强安全性的产品,同时也是首次对可节约高达75%处理器功耗的ARM智能能量管理(ARM Intelligent Energy Manager)进行一体化支持。ARM1176JZ-S和ARM1176JZF-S内核基于ARMv6指令集体系结构,主要为服务供应商和运营商所提供的新一代消费电子装置的电子商务和安全的网络下载提供支持。

CoreSight技术建于ARM Embedded Trace Macrocell (ETM)实时跟踪模块中,为完整的片上系统(SoC)设计提供最全面的调试、跟踪技术方案,通过最小端口可获得全面的系统可见度,并为开发者大大节约了产品上市时间。ARM CoreSight技术提供了最标准的调试和跟踪性能,适用于各种内核和复杂外设,可对核内指令和数据进行追踪。该技术为半导体制造商和工具供应商建立了可真正协同工作的系统调试标准,可满足嵌入式开发者和半导体制造商的各种需求,如以最低的成本来提供全面的系统可见度,从而降低处理器成本。

ARM公司嵌入式内核经理Richard Phelan先生说:"随着竞争的日益激烈,系统开发者必须以低廉的费用实现嵌入式系统的高性能并延长电池的待机时间。ARM1156T2-S和ARM1156T2F-S内核在0.13μ工艺下新的操作频率高达550MHz,拥有高效的Thumb-2指令集和AMBA 3.0 AXI系统总线,ARM1156T2-S和ARM1156T2F-S内核为合作伙伴们提供了所需的知识产权(IP),满足各种新兴的嵌入式控制应用产品的高性能需求。"

ARM CPU产品经理David Cormie先生评论说:"为了进一步提高新一代消费电子装置和无线装置的安全性,运营商、服务商和消费者的重要数据的保护、隐私保护需要一个可信赖的计算环境。ARM1176JZ-S和ARM1176JZF-S内核及PrimeXsys平台结合了ARM TrustZone技术,为计算装置提供了理想的可信赖基础。系统设计者首次在芯片核心部分运用TrustZone技术来解决安全性问题。用户将拥有更多的下载选择,运营商将增加营业额收入,他们都无需担心网络的安全问题。"

ARM1176JZ-S和ARM1176JZF-S内核、PrimeXsys平台提供了安全的低功耗设计,含有AMBA 3.0 AXI,可对频率和电压变化进行控制;系统级TrustZone软硬件参考设计。两个新内核中集成了ARM Jazelle技术,可加快嵌入式Java执行。ARM1176JZF-S内核包含一个浮点协处理器,极适合用于嵌入式3D图像应用产品。两个新内核的标准配置中都含有ARM-Synopsys RTL to GDSII参考技术方案,都是可综合的,在0.13μ工艺中,最低频率可达333-550MHz。PrimeXsys平台包含ARM CoreSight?技术,提供了世界领先的调试和跟踪技术方案。

ARM CoreSight技术可快速地对不同地软件进行调试,通过对多核和AMBA?总线的情况进行同时跟踪。此外,同时对多核进行暂停和调试,CoreSight技术可对AMBA上的存储器和外设进行调试,无需暂停处理器工作,达到不易做到的实时开发。ARM CoreSight技术拥有更高的压缩率,为半导体制造商们提供了对新的更高频处理器进行调试、跟踪的技术方案。使用CoreSight技术,制造商们可通过减少调试所需的管脚、减少片上跟踪缓存所需的芯片面积等手段来降低生产成本。

1、本站所有文本、信息、视频文件等,仅代表本站观点或作者本人观点,请网友谨慎参考使用。

2、本站信息均为作者提供和网友推荐收集整理而来,仅供学习和研究使用。

3、对任何由于使用本站内容而引起的诉讼、纠纷,本站不承担任何责任。

4、如有侵犯你版权的,请来信(邮箱:baike52199@gmail.com)指出,核实后,本站将立即删除。

下一篇 ARM Cortex-A8

上一篇 ARM9